# MOS INTEGRATED CIRCUIT $\mu$ **PD16682**

### 1/65 DUTY LCD CONTROLLER/DRIVER WITH ON-CHIP RAM

#### DESCRIPTION

The  $\mu$  PD16682 is a LCD controller/driver that includes enough RAM capacity to drive full-dot LCD. Each chip can drive a full-dot LCD consisting of up to 132 x 65 dots.

This chip is suitable for cellular phones, Japanese or Chinese-language pagers, and other devices that display Japanese or Chinese characters using either 16 x 16 or 12 x 12 dots per character.

#### FEATURES

- LCD controller/driver with on-chip display RAM

- Able to operate using +3-V single power supply

- On-chip booster circuit: switchable between 3x and 4x modes

- RAM for dot displays: 132 x 65 bits

- Outputs : 132 segments, 65 commons

- Serial or 8-bit parallel data inputs (switchable between 80 series and 68 series MPUs)

- On-chip divider resistor

- Selectable bias settings (can be set as 1/9 bias or 1/7 bias)

- On-chip oscillation circuit

#### **ORDERING INFORMATION**

| Part number                             | Package                                                  |

|-----------------------------------------|----------------------------------------------------------|

| $\mu$ PD16682W-xxx <sup>Note</sup>      | Wafer                                                    |

| $\mu$ PD16682P-xxx <sup>Note</sup>      | Chip                                                     |

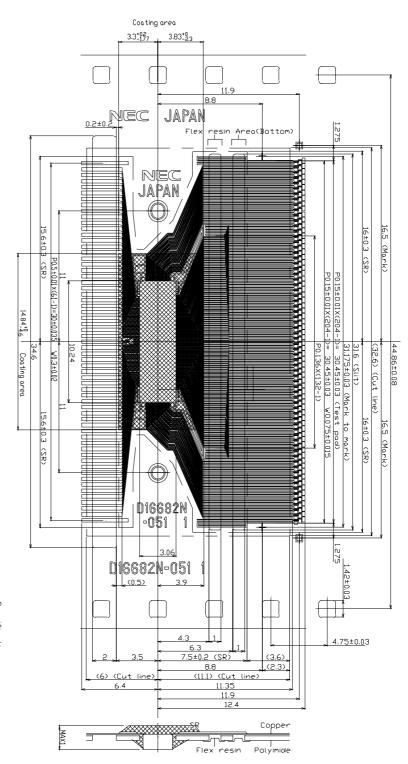

| $\mu$ PD16682N-xxx <sup>Note</sup> -051 | Standard TCP (output OLB: 0.15-mm pitch), for evaluation |

**Note** The following four temperature gradients can be selected.

-001: -0.05 % / °C -002: -0.1 % / °C -003: -0.15 % / °C -004: 0 % / °C

**Remark** Purchasing the above chip/wafer entails exchange of documents such as a separate memorandum or product quality, so please contact one of our sales representative.

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

Vr

HPM

$V_{LC1}$

VLC2 VLC3 VLC4 VLC5

$V_{DD2}$ IRS

$V_{\text{LCD}}$

Ν

<u>.</u>

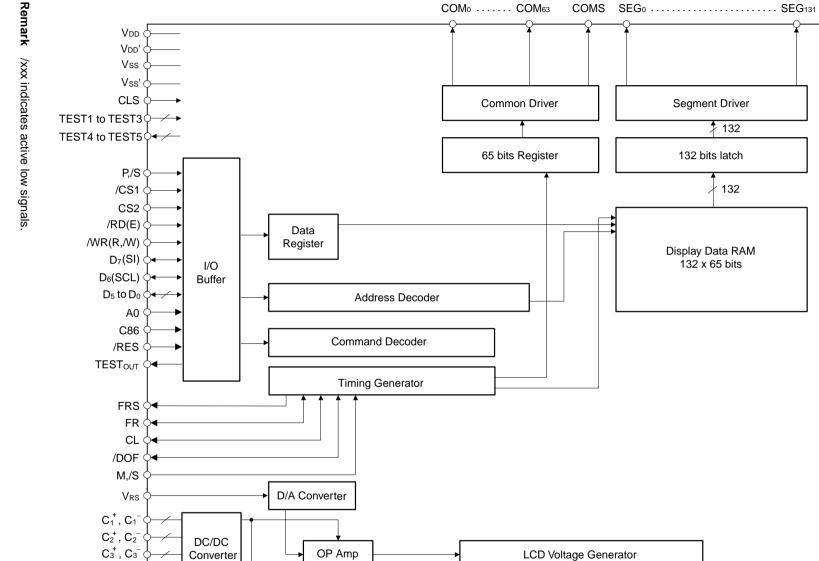

**BLOCK DIAGRAM**

132

132

132 bits latch

132 x 65 bits

μ PD16682

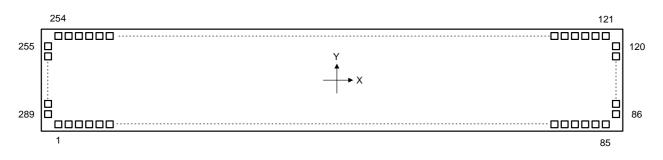

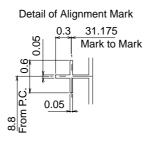

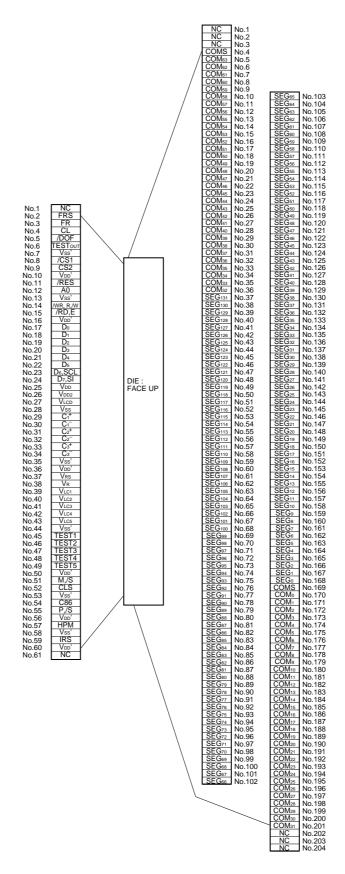

#### 2. PIN CONFIGURATION (Pad Layout)

Chip Size: 2.66 mm x 9.84 mm

| Table 2–1. Pad Layout (1/3) |                                  |         |         |             |            |                   |              |         |             |  |  |

|-----------------------------|----------------------------------|---------|---------|-------------|------------|-------------------|--------------|---------|-------------|--|--|

| Pad<br>No.                  | Pad Name                         | X [μ m] | Υ [μ m] | Pad<br>Type | Pad<br>No. | Pad Name          | X [μ m]      | Υ [μ m] | Pad<br>Type |  |  |

| 1                           | DUMMY1                           | -3804   | -1198   | С           | 59         | VLC2              | 1448         | -1198   | В           |  |  |

| 2                           | FRS                              | -3682   | -1198   | В           | 60         | VLC2              | 1538         | -1198   | В           |  |  |

| 3                           | FR                               | -3592   | -1198   | В           | 61         | VLC3              | 1628         | -1198   | В           |  |  |

| 4                           | CL                               | -3502   | -1198   | В           | 62         | VLC3              | 1718         | -1198   | В           |  |  |

| 5                           | /DOF                             | -3412   | -1198   | В           | 63         | VLC4              | 1808         | -1198   | В           |  |  |

| 6                           | TESTOUT                          | -3322   | -1198   | В           | 64         | VLC4              | 1898         | -1198   | В           |  |  |

| 7                           | Vss'                             | -3232   | -1198   | В           | 65         | VLC5              | 1988         | -1198   | В           |  |  |

| 8                           | /CS1                             | -3142   | -1198   | В           | 66         | VLC5              | 2078         | -1198   | В           |  |  |

| 9                           | CS2                              | -3052   | -1198   | В           | 67         | Vss'              | 2168         | -1198   | В           |  |  |

| 10                          | V <sub>DD</sub> '                | -2962   | -1198   | B           | 68         | Vss'              | 2258         | -1198   | B           |  |  |

| 11                          | /RES                             | -2872   | -1198   | B           | 69         | TEST1             | 2348         | -1198   | B           |  |  |

| 12                          | A0                               | -2782   | -1198   | B           | 70         | TEST2             | 2438         | -1198   | B           |  |  |

| 13                          | Vss'                             | -2692   | -1198   | B           | 71         | TEST3             | 2528         | -1198   | B           |  |  |

| 14                          | /WR(R,/W)                        | -2602   | -1198   | B           | 72         | TEST4             | 2618         | -1198   | B           |  |  |

| 14                          | /WR(R,/W)<br>/RD(E)              | -2512   | -1198   | B           | 72         | TEST5             | 2018         | -1198   | B           |  |  |

|                             |                                  |         |         | -           |            |                   |              |         |             |  |  |

| 16                          | Vdd'                             | -2422   | -1198   | B           | 74         | VDD'              | 2798<br>2888 | -1198   | B           |  |  |

| 17                          | D <sub>0</sub>                   | -2332   | -1198   | В           | 75         | M,/S              |              | -1198   | B           |  |  |

| 18                          | D1                               | -2242   | -1198   | B           | 76         | CLS               | 2978         | -1198   | B           |  |  |

| 19                          | D2                               | -2152   | -1198   | В           | 77         | Vss'              | 3068         | -1198   | B           |  |  |

| 20                          | D <sub>3</sub>                   | -2062   | -1198   | В           | 78         | C86               | 3158         | -1198   | В           |  |  |

| 21                          | D4                               | -1972   | -1198   | В           | 79         | P,/S              | 3248         | –1198   | В           |  |  |

| 22                          | D₅                               | -1882   | -1198   | В           | 80         | VDD'              | 3338         | -1198   | В           |  |  |

| 23                          | D <sub>6</sub> (SCL)             | -1792   | -1198   | В           | 81         | HPM               | 3428         | –1198   | В           |  |  |

| 24                          | D7(SI)                           | -1702   | -1198   | В           | 82         | Vss'              | 3518         | –1198   | В           |  |  |

| 25                          | Vdd                              | -1612   | -1198   | В           | 83         | IRS               | 3608         | –1198   | В           |  |  |

| 26                          | Vdd                              | -1522   | -1198   | В           | 84         | Vdd'              | 3698         | -1198   | В           |  |  |

| 27                          | Vdd                              | -1432   | -1198   | В           | 85         | DUMMY2            | 3820         | -1198   | С           |  |  |

| 28                          | VDD2                             | -1342   | -1198   | В           | 86         | DUMMY3            | 4788         | -1032   | С           |  |  |

| 29                          | VDD2                             | -1252   | -1198   | В           | 87         | COM <sub>31</sub> | 4788         | -940    | Α           |  |  |

| 30                          | Vdd2                             | -1162   | -1198   | В           | 88         | COM <sub>30</sub> | 4788         | -880    | Α           |  |  |

| 31                          | Vdd2                             | -1072   | -1198   | В           | 89         | COM <sub>29</sub> | 4788         | -820    | Α           |  |  |

| 32                          | VLCD                             | -982    | -1198   | В           | 90         | COM <sub>28</sub> | 4788         | -760    | Α           |  |  |

| 33                          | VLCD                             | -892    | -1198   | В           | 91         | COM <sub>27</sub> | 4788         | -700    | Α           |  |  |

| 34                          | VLCD                             | -802    | -1198   | В           | 92         | COM <sub>26</sub> | 4788         | -640    | Α           |  |  |

| 35                          | Vss                              | -712    | -1198   | В           | 93         | COM <sub>25</sub> | 4788         | -580    | Α           |  |  |

| 36                          | Vss                              | -622    | -1198   | В           | 94         | COM <sub>24</sub> | 4788         | -520    | Α           |  |  |

| 37                          | Vss                              | -532    | -1198   | В           | 95         | COM <sub>23</sub> | 4788         | -460    | A           |  |  |

| 38                          | C1 <sup>+</sup>                  | -442    | -1198   | В           | 96         | COM <sub>22</sub> | 4788         | -400    | A           |  |  |

| 39                          | C1 <sup>+</sup>                  | -352    | -1198   | B           | 97         | COM <sub>21</sub> | 4788         | -340    | A           |  |  |

| 40                          | C1 <sup>-</sup>                  | -262    | -1198   | B           | 98         | COM <sub>20</sub> | 4788         | -280    | A           |  |  |

| 40                          | $C_1^-$                          | -172    | -1198   | B           | 99         |                   | 4788         | -220    | A           |  |  |

| 41                          | $C_2^+$                          | -82     | -1198   | B           | 100        |                   | 4788         | -160    | A           |  |  |

| 42                          | $C_2^+$                          | 8       |         | B           | 100        |                   | 4788         | -100    |             |  |  |

| 43                          | C <sub>2</sub><br>C <sub>2</sub> |         | -1198   | В           |            |                   |              |         | A           |  |  |

|                             | C <sub>2</sub><br>C <sub>2</sub> | 98      | -1198   | -           | 102        |                   | 4788         | -40     | A           |  |  |

| 45                          |                                  | 188     | -1198   | B           | 103        |                   | 4788         | 20      | A           |  |  |

| 46                          | $C_{3}^{+}$                      | 278     | -1198   | B           | 104        |                   | 4788         | 80      | A           |  |  |

| 47                          | $C_3^+$                          | 368     | -1198   | B           | 105        |                   | 4788         | 140     | A           |  |  |

| 48                          | C <sub>3</sub> -                 | 458     | -1198   | В           | 106        |                   | 4788         | 200     | A           |  |  |

| 49                          | C3 <sup>-</sup>                  | 548     | -1198   | В           | 107        |                   | 4788         | 260     | A           |  |  |

| 50                          | Vss'                             | 638     | -1198   | В           | 108        |                   | 4788         | 320     | A           |  |  |

| 51                          | Vdd'                             | 728     | -1198   | В           | 109        | COM <sub>9</sub>  | 4788         | 380     | A           |  |  |

| 52                          | Vdd'                             | 818     | –1198   | В           | 110        | COM8              | 4788         | 440     | A           |  |  |

| 53                          | Vrs                              | 908     | -1198   | В           | 111        | COM <sub>7</sub>  | 4788         | 500     | А           |  |  |

| 54                          | Vrs                              | 998     | -1198   | В           | 112        | COM <sub>6</sub>  | 4788         | 560     | А           |  |  |

| 55                          | VR                               | 1088    | -1198   | В           | 113        | COM <sub>5</sub>  | 4788         | 620     | Α           |  |  |

| 56                          | VR                               | 1178    | -1198   | В           | 114        | COM <sub>4</sub>  | 4788         | 680     | Α           |  |  |

| 57                          | VLC1                             | 1268    | -1198   | В           | 115        | COM <sub>3</sub>  | 4788         | 740     | А           |  |  |

| 58                          | VLC1                             | 1358    | -1198   | В           | 116        | COM <sub>2</sub>  | 4788         | 800     | Α           |  |  |

Table 2–1. Pad Layout (1/3)

| Pad<br>No. | Pad Name          | Χ [μ m] | Υ [μ m] | Pad<br>Type | Pad<br>No. | Pad Name          | Χ [μ m]      | Υ [μ m] | Pad<br>Type |

|------------|-------------------|---------|---------|-------------|------------|-------------------|--------------|---------|-------------|

| 117        | COM <sub>1</sub>  | 4788    | 860     | A           | 175        | SEG53             | 750          | 1198    | A           |

| 118        |                   | 4788    | 920     | Α           | 176        | SEG <sub>54</sub> | 690          | 1198    | Α           |

| 119        | COMS              | 4788    | 980     | Α           | 177        | SEG55             | 630          | 1198    | Α           |

| 120        | DUMMY4            | 4788    | 1073    | С           | 178        | SEG <sub>56</sub> | 570          | 1198    | Α           |

| 121        | DUMMY5            | 4023    | 1198    | С           | 179        | SEG57             | 510          | 1198    | Α           |

| 122        | SEG <sub>0</sub>  | 3930    | 1198    | Α           | 180        | SEG <sub>58</sub> | 450          | 1198    | Α           |

| 123        | SEG1              | 3870    | 1198    | Α           | 181        | SEG <sub>59</sub> | 390          | 1198    | А           |

| 124        | SEG <sub>2</sub>  | 3810    | 1198    | Α           | 182        | SEG <sub>60</sub> | 330          | 1198    | Α           |

| 125        | SEG <sub>3</sub>  | 3750    | 1198    | Α           | 183        | SEG <sub>61</sub> | 270          | 1198    | А           |

| 126        | SEG <sub>4</sub>  | 3690    | 1198    | Α           | 184        | SEG <sub>62</sub> | 210          | 1198    | Α           |

| 127        | SEG₅              | 3630    | 1198    | Α           | 185        | SEG <sub>63</sub> | 150          | 1198    | Α           |

| 128        | SEG <sub>6</sub>  | 3570    | 1198    | Α           | 186        | SEG <sub>64</sub> | 90           | 1198    | Α           |

| 129        | SEG7              | 3510    | 1198    | A           | 187        | SEG <sub>65</sub> | 30           | 1198    | A           |

| 130        | SEG8              | 3450    | 1198    | A           | 188        | SEG <sub>66</sub> | -30          | 1198    | A           |

| 131        | SEG <sub>9</sub>  | 3390    | 1198    | A           | 189        | SEG <sub>67</sub> | -90          | 1198    | A           |

| 132        | SEG10             | 3330    | 1198    | A           | 190        | SEG <sub>68</sub> | -150         | 1198    | A           |

| 133        | SEG11             | 3270    | 1198    | A           | 191        | SEG <sub>69</sub> | -210         | 1198    | A           |

| 133        | SEG <sub>12</sub> | 3210    | 1198    | A           | 192        | SEG70             | -270         | 1198    | A           |

| 134        | SEG <sub>12</sub> | 3150    | 1198    | A           | 192        | SEG71             | -330         | 1198    | A           |

| 136        | SEG <sub>14</sub> | 3090    | 1198    | A           | 193        | SEG72             | -390         | 1198    | A           |

| 130        | SEG14<br>SEG15    | 3030    | 1198    | A           | 194        | SEG72<br>SEG73    | -390<br>-450 | 1198    | A           |

| 137        | SEG <sub>16</sub> | 2970    | 1198    | A           | 196        | SEG74             | -510         | 1198    | A           |

| 139        | SEG17             | 2970    | 1198    | A           | 190        | SEG75             | -570         | 1198    | A           |

| 140        | SEG17<br>SEG18    | 2850    | 1198    | A           | 197        | SEG76             | -630         | 1198    | A           |

| 140        | SEG18<br>SEG19    | 2790    | 1198    | A           | 198        | SEG76<br>SEG77    | _690         | 1198    | A           |

|            |                   |         |         |             |            |                   |              |         |             |

| 142        | SEG <sub>20</sub> | 2730    | 1198    | A           | 200        | SEG78             | -750         | 1198    | A           |

| 143        | SEG <sub>21</sub> | 2670    | 1198    | A           | 201        | SEG79             | -810         | 1198    | A           |

| 144        | SEG <sub>22</sub> | 2610    | 1198    | A           | 202        | SEG80             | -870         | 1198    | A           |

| 145        | SEG <sub>23</sub> | 2550    | 1198    | A           | 203        | SEG <sub>81</sub> | -930         | 1198    | A           |

| 146        | SEG <sub>24</sub> | 2490    | 1198    | A           | 204        | SEG <sub>82</sub> | -990         | 1198    | A           |

| 147        | SEG <sub>25</sub> | 2430    | 1198    | A           | 205        | SEG83             | -1050        | 1198    | A           |

| 148        | SEG <sub>26</sub> | 2370    | 1198    | Α           | 206        | SEG <sub>84</sub> | -1110        | 1198    | A           |

| 149        | SEG <sub>27</sub> | 2310    | 1198    | Α           | 207        | SEG <sub>85</sub> | -1170        | 1198    | Α           |

| 150        | SEG <sub>28</sub> | 2250    | 1198    | A           | 208        | SEG <sub>86</sub> | -1230        | 1198    | A           |

| 151        | SEG <sub>29</sub> | 2190    | 1198    | A           | 209        | SEG <sub>87</sub> | -1290        | 1198    | A           |

| 152        | SEG <sub>30</sub> | 2130    | 1198    | A           | 210        | SEG88             | -1350        | 1198    | A           |

| 153        | SEG31             | 2070    | 1198    | A           | 211        | SEG89             | -1410        | 1198    | A           |

| 154        | SEG <sub>32</sub> | 2010    | 1198    | A           | 212        | SEG90             | -1470        | 1198    | A           |

| 155        | SEG <sub>33</sub> | 1950    | 1198    | A           | 213        | SEG91             | –1530        | 1198    | Α           |

|            | SEG <sub>34</sub> | 1890    | 1198    | А           |            | SEG <sub>92</sub> | -1590        | 1198    | А           |

| 157        | SEG35             | 1830    | 1198    | A           | 215        | SEG93             | -1650        | 1198    | A           |

| 158        | SEG <sub>36</sub> | 1770    | 1198    | А           | 216        | SEG <sub>94</sub> | –1710        | 1198    | А           |

| 159        | SEG <sub>37</sub> | 1710    | 1198    | Α           | 217        | SEG <sub>95</sub> | -1770        | 1198    | Α           |

| 160        | SEG <sub>38</sub> | 1650    | 1198    | Α           | 218        | SEG <sub>96</sub> | -1830        | 1198    | Α           |

| 161        | SEG <sub>39</sub> | 1590    | 1198    | Α           | 219        | SEG <sub>97</sub> | -1890        | 1198    | А           |

| 162        | SEG <sub>40</sub> | 1530    | 1198    | А           | 220        | SEG <sub>98</sub> | -1950        | 1198    | Α           |

| 163        | SEG <sub>41</sub> | 1470    | 1198    | А           | 221        | SEG <sub>99</sub> | -2010        | 1198    | А           |

| 164        | SEG <sub>42</sub> | 1410    | 1198    | Α           | 222        | SEG100            | -2070        | 1198    | Α           |

| 165        | SEG <sub>43</sub> | 1350    | 1198    | Α           | 223        | SEG101            | -2130        | 1198    | Α           |

| 166        | SEG44             | 1290    | 1198    | Α           | 224        | SEG102            | -2190        | 1198    | Α           |

| 167        | SEG <sub>45</sub> | 1230    | 1198    | Α           | 225        | SEG103            | -2250        | 1198    | Α           |

| 168        | SEG <sub>46</sub> | 1170    | 1198    | Α           | 226        | SEG104            | -2310        | 1198    | Α           |

| 169        | SEG <sub>47</sub> | 1110    | 1198    | Α           | 227        | SEG105            | -2370        | 1198    | Α           |

| 170        | SEG <sub>48</sub> | 1050    | 1198    | Α           | 228        | SEG106            | -2430        | 1198    | Α           |

| 171        | SEG <sub>49</sub> | 990     | 1198    | A           | 229        | SEG107            | -2490        | 1198    | A           |

| 172        | SEG <sub>50</sub> | 930     | 1198    | A           | 230        | SEG108            | -2550        | 1198    | A           |

| 173        | SEG <sub>51</sub> | 870     | 1198    | A           | 231        | SEG109            | -2610        | 1198    | A           |

| 174        | SEG <sub>52</sub> | 810     | 1198    | A           | 232        | SEG110            | -2670        | 1198    | A           |

Table 2–1. Pad Layout (2/3)

| Pad<br>No. | Pad Name           | Χ [μ m] | Υ [ <i>μ</i> m] | Pad<br>Type |

|------------|--------------------|---------|-----------------|-------------|

| 233        | SEG111             | -2730   | 1198            | A           |

| 234        | SEG112             | -2790   | 1198            | Α           |

| 235        | SEG113             | -2850   | 1198            | Α           |

| 236        | SEG114             | -2910   | 1198            | Α           |

| 237        | SEG115             | -2970   | 1198            | Α           |

| 238        | SEG116             | -3030   | 1198            | Α           |

| 239        | SEG117             | -3090   | 1198            | А           |

| 240        | SEG118             | -3150   | 1198            | А           |

| 241        | SEG119             | -3210   | 1198            | А           |

| 242        | SEG <sub>120</sub> | -3270   | 1198            | Α           |

| 243        | SEG <sub>121</sub> | -3330   | 1198            | А           |

| 244        | SEG <sub>122</sub> | -3390   | 1198            | Α           |

| 245        | SEG <sub>123</sub> | -3450   | 1198            | А           |

| 246        | SEG <sub>124</sub> | -3510   | 1198            | А           |

| 247        | SEG <sub>125</sub> | -3570   | 1198            | Α           |

| 248        | SEG <sub>126</sub> | -3630   | 1198            | А           |

| 249        | SEG127             | -3690   | 1198            | А           |

| 250        | SEG <sub>128</sub> | -3750   | 1198            | Α           |

| 251        | SEG <sub>129</sub> | -3810   | 1198            | А           |

| 252        | SEG <sub>130</sub> | -3870   | 1198            | Α           |

| 253        | SEG131             | -3930   | 1198            | Α           |

| 254        | DUMMY6             | -4022   | 1198            | С           |

| 255        | DUMMY7             | -4788   | 1032            | С           |

| 256        | COM <sub>32</sub>  | -4788   | 940             | Α           |

| 257        | COM <sub>33</sub>  | -4788   | 880             | А           |

| 258        | COM <sub>34</sub>  | -4788   | 820             | Α           |

| 259        | COM35              | -4788   | 760             | Α           |

| 260        | COM <sub>36</sub>  | -4788   | 700             | А           |

| 261        | COM <sub>37</sub>  | -4788   | 640             | А           |

| 262        | COM <sub>38</sub>  | -4788   | 580             | Α           |

| 263        | COM <sub>39</sub>  | -4788   | 520             | А           |

| 264        | COM <sub>40</sub>  | -4788   | 460             | Α           |

| 265        | COM <sub>41</sub>  | -4788   | 400             | А           |

| 266        | COM <sub>42</sub>  | -4788   | 340             | Α           |

| 267        | COM <sub>43</sub>  | -4788   | 280             | Α           |

| 268        | COM44              | -4788   | 220             | А           |

| 269        | COM <sub>45</sub>  | -4788   | 160             | Α           |

| 270        | COM <sub>46</sub>  | -4788   | 100             | Α           |

| 271        | COM47              | -4788   | 40              | A           |

| 272        | COM <sub>48</sub>  | -4788   | -20             | А           |

| 273        | COM <sub>49</sub>  | -4788   | -80             | Α           |

| 274        | COM <sub>50</sub>  | -4788   | -140            | А           |

| 275        | COM <sub>51</sub>  | -4788   | -200            | Α           |

| 276        | COM <sub>52</sub>  | -4788   | -260            | А           |

| 277        | COM <sub>53</sub>  | -4788   | -320            | A           |

| 278        | COM <sub>54</sub>  | -4788   | -380            | А           |

| 279        | COM55              | -4788   | -440            | Α           |

| 280        | COM <sub>56</sub>  | -4788   | -500            | А           |

| 281        | COM <sub>57</sub>  | -4788   | -560            | А           |

| 282        | COM <sub>58</sub>  | -4788   | -620            | А           |

| 283        | COM <sub>59</sub>  | -4788   | -680            | А           |

| 284        |                    | -4788   | -740            | A           |

| 285        | COM <sub>61</sub>  | -4788   | -800            | A           |

| 286        | COM62              | -4788   | -860            | A           |

| 287        | COM <sub>63</sub>  | -4788   | -920            | A           |

| 288        | COMS               | -4788   | -980            | A           |

| 289        | DUMMY8             | -4788   | -1073           | C           |

| Table 2–1. | Pad Layout | (3/3) |

|------------|------------|-------|

|------------|------------|-------|

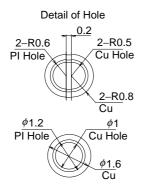

Remark Pad Type A:

Pad size(Al): 47 x 105  $\mu$  m<sup>2</sup>(TYP.) Bump size: 35 x 92.5  $\mu$  m<sup>2</sup>(TYP.) Bump height: 17  $\mu$  m(TYP.) Pad Type B:

Pad size(Al): 75 x 105  $\mu$  m<sup>2</sup>(TYP.) Bump size: 67 x 92.5  $\mu$  m<sup>2</sup>(TYP.)

Bump height: 17  $\mu$  m(TYP.)

Pad Type C:

Pad size(Al): 118 x 105  $\mu$  m<sup>2</sup>(TYP.) Bump size: 110 x 92.5  $\mu$  m<sup>2</sup>(TYP.) Bump height: 17  $\mu$  m(TYP.)

#### 3. PIN DESCRIPTIONS

#### 3.1 Power Supply System Pins

| Pin Symbol                                                                                                  | Pin Name                                  | Pad No.                      | I/O | Function Description                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vdd                                                                                                         | Logic power supply pins                   | 25 to 27                     | —   | Power supply pins for logic. Apply the logic power supply voltage from an external source.                                                                                                                                                          |

| Vdd2                                                                                                        | Booster circuit power<br>supply pins      | 28 to 31                     | —   | Power supply pins for booster circuit. Apply the booster circuit power supply voltage from an external source.                                                                                                                                      |

| Vss                                                                                                         | Logic/driver ground pins                  | 35 to 37                     | —   | Ground pins for logic and driver circuit. Connect these pins to an external ground.                                                                                                                                                                 |

| Vlcd                                                                                                        | Driver power supply pins                  | 32 to 34                     | _   | Power supply pins for driver. Output pins for internal booster circuit.<br>Connect a $1-\mu$ F capacitor for boosting between these pins and the GND pins.<br>If not using the internal booster circuit, a direct driver power supply can be input. |

| Vdd'                                                                                                        | Power supply pins for fixed mode pins     | 10,16,51,<br>52,74,80,<br>84 | —   | These power supply pins are used to set the mode pins as fixed.                                                                                                                                                                                     |

| Vss'                                                                                                        | Ground pins for fixed mode pins           | 7,13,50,<br>67,68,77,<br>82  | _   | These ground pins are used to set the mode pins as fixed.                                                                                                                                                                                           |

| VLC1 to VLC5                                                                                                | Reference power supply<br>pins for driver | 57 to 66                     | —   | These are reference power supply pins for the LCD driver.<br>Connect a smoothing capacitor if an internal bias has been<br>selected.                                                                                                                |

| C1 <sup>+</sup> , C1 <sup>-</sup><br>C2 <sup>+</sup> , C2 <sup>-</sup><br>C3 <sup>+</sup> , C3 <sup>-</sup> | Capacitor connection pins                 | 38 to 49                     | _   | These are capacitor connection pins for the booster circuit. Connect a $1-\mu$ F capacitor.                                                                                                                                                         |

#### 3.2 Logic System Pins (1/2)

| Pin Symbol | Pin Name                   | Pad No.  | I/O              | Function Description                                                                                                                                                                                                                                                                                                                                           |

|------------|----------------------------|----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P,/S       | Select data input          | 79       | Input            | This pin is used to select between parallel data input and serial data input.<br>P,/S = H: Parallel data input<br>P,/S = L: Serial data input<br>This setting cannot be switched after power-on. For details, see                                                                                                                                              |

| /CS1,CS2   | Chip select                | 8,9      | Input            | <ul> <li>5. DESCRIPTION OF FUNCTIONS.</li> <li>These pins are used for the chip select signal. When /CS1 = L<br/>and CS2 = H, this signal is active and can be used for I/O of data<br/>and commands.</li> </ul>                                                                                                                                               |

| /RD(E)     | Read (enable)              | 15       | Input            | <ul> <li>When connected to 80 series MPU : active low</li> <li>This pin connects the 80 series MPU's RD signal. Data bus output status is set when this signal is low.</li> <li>When connected to 68 series MPU : active high</li> <li>It is used as the enable clock input pin for the 68 series MPU.</li> </ul>                                              |

| /WR(R,/W)  | Write (read/write)         | 14       | Input            | <ul> <li>When connected to 80 series MPU: active low</li> <li>When connects the 80 series MPU's /WR signal. Signals on the data bus are latched at the rising edge of the /WR signal.</li> <li>When connected to 68 series MPU</li> <li>This pin is an input pin for read/write control signals.</li> <li>R,/W = H : Read</li> <li>R,/W = L : Write</li> </ul> |

| C86        | Interface select           | 78       | Input            | This pin is used to select the MPU interface.<br>C86 = H : 68 series MPU interface<br>C86 = L : 80 series MPU interface                                                                                                                                                                                                                                        |

| D₀ to D₅   | Data bus                   | 17 to 22 | Input<br>/Output | When used with a parallel interface, these pins correspond to data bus bits $D_0$ to $D_5$ .<br>When used with a serial interface, they are pulled down internally.                                                                                                                                                                                            |

| D6 (SCL)   | Data bus/serial clock      | 23       | Input<br>/Output | When used with a parallel interface, this pin corresponds to data<br>bus bit D <sub>6</sub> .<br>When used with a serial interface, it is a serial clock input pin.                                                                                                                                                                                            |

| D7 (SI)    | Data bus/serial data input | 24       | Input<br>/Output | When used with a parallel interface, this pin corresponds to data<br>bus bit D7.<br>When used with a serial interface, it is a serial data input pin.                                                                                                                                                                                                          |

| AO         | Data command               | 12       | Input            | This pin is connected to the LSB in the ordinary MPU address<br>bus to distinguish between data and commands.<br>A0 = H : Indicates that display data exists in bits D <sub>0</sub> to D <sub>7</sub> .<br>A0 = L : Indicates that display control commands exist in bits D <sub>0</sub><br>to D <sub>7</sub> .                                                |

| TESTout    | Test output                | 6        | Output           | This pin is used as a test output. Leave this pin open when used for this purpose.                                                                                                                                                                                                                                                                             |

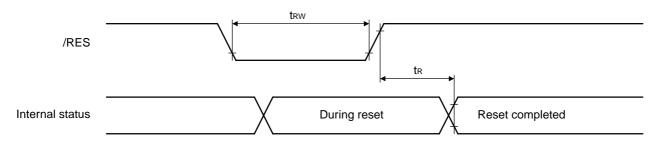

| /RES       | Reset                      | 11       | Input            | This pin is used to perform an internal reset when at low level.                                                                                                                                                                                                                                                                                               |

| CLK        | Clock select               | 76       | Input            | This pin is used to select the valid/invalid setting for the display clock's on-chip oscillation circuit.<br>CLS = H : On-chip oscillation circuit is valid<br>CLS = L : On-chip oscillation circuit is invalid (external input)<br>When CLS = L, a display clock is input via the CL pin.                                                                     |

#### 3.2 Logic System Pins (2/2)

|             |                           |          |                  | 1                                                               |                      |             |            |                       |                 |            |          |

|-------------|---------------------------|----------|------------------|-----------------------------------------------------------------|----------------------|-------------|------------|-----------------------|-----------------|------------|----------|

| Pin Symbol  | Pin Name                  | Pad No.  | I/O              | Function Description                                            |                      |             |            |                       |                 |            |          |

| FR          | Frame signal              | 3        | Input            |                                                                 | is used              | as an I/    | O pin for  | the LCE               | o's AC co       | onversio   | n        |

|             |                           |          | /Output          | signal.                                                         |                      |             |            |                       |                 |            |          |

|             |                           |          |                  | This pin is used (along with the FRS pin) for the static drive. |                      |             |            |                       |                 |            | /e.      |

| FRS         | Static signal             | 2        | Output           | This pin                                                        | is used              | as an o     | utput pin  | for the s             | static driv     | /e.        |          |

|             |                           |          |                  | This pin                                                        | is used              | (along v    | vith the F | FR pin) fo            | or the sta      | atic drive |          |

| M,/S        | Master/Slave              | 75       | Input            | •                                                               |                      |             |            | or slave              | •               |            |          |

|             |                           |          |                  | -                                                               | -                    |             |            | CD are o              |                 | -          |          |

|             |                           |          |                  |                                                                 | nd are ir<br>CD bloc |             | ng slave   | mode to               | ensure          | synchro    | nizatior |

|             |                           |          |                  |                                                                 |                      | ter opera   | ation mo   | de                    |                 |            |          |

|             |                           |          |                  |                                                                 |                      | e operati   |            |                       |                 |            |          |

|             |                           |          |                  |                                                                 |                      |             |            | on the sta            | atus of th      | ne M./S a  | and      |

|             |                           |          |                  | CLS pin                                                         | -                    | ,           |            |                       |                 | - ,        |          |

|             |                           |          |                  | M,/S                                                            | CLS                  | Oscillation | Power      | CL                    | FR              | FRS        | /DOF     |

|             |                           |          |                  |                                                                 |                      | Circuit     | supply     |                       |                 |            |          |

|             |                           |          |                  |                                                                 |                      |             | circuit    |                       |                 |            |          |

|             |                           |          |                  | н                                                               | Н                    | Valid       | Valid      | Output                | Output          | Output     | Outpu    |

|             |                           |          |                  |                                                                 | L                    | Invalid     | Valid      | Input                 | Output          | Output     | Output   |

|             |                           |          |                  | L                                                               | Н                    | Invalid     | Invalid    | Input                 | Input           | Hi-Z       | Input    |

|             |                           |          |                  |                                                                 | L                    | Invalid     | Invalid    | Input                 | Input           | Hi-Z       | Input    |

| CL          | Display clock input       | 4        | Input            | This pin                                                        | is used              |             |            | ock I/O               |                 |            |          |

| -           |                           |          | /Output          |                                                                 |                      |             |            | e M,/S a              |                 |            |          |

|             |                           |          | /                | M,/S                                                            | CLS                  | CL          | Ī          |                       |                 |            |          |

|             |                           |          |                  | н                                                               | Н                    | Output      |            |                       |                 |            |          |

|             |                           |          |                  |                                                                 | L                    | Input       |            |                       |                 |            |          |

|             |                           |          |                  | L                                                               | H                    |             |            |                       |                 |            |          |

|             |                           |          |                  |                                                                 |                      | Input       |            |                       |                 |            |          |

|             |                           |          |                  |                                                                 | L                    | Input       | <u> </u>   |                       |                 |            |          |

|             |                           |          |                  |                                                                 |                      |             | naster or  | slave m               | ode, cor        | nect it to | o the    |

| /DOF        | Blink control             | 5        | Input            |                                                                 | onding (             |             | ol blinkir | ng in the             |                 |            |          |

| /DOF        | Blink control             | 5        | Input<br>/Output |                                                                 | H : Out              |             |            | ig in the             | LCD.            |            |          |

|             |                           |          | /Output          |                                                                 | L : Inpu             |             |            |                       |                 |            |          |

|             |                           |          |                  |                                                                 |                      |             | naster or  | slave m               | ode. cor        | nect it to | o the    |

|             |                           |          |                  |                                                                 | -                    | DOF pin     |            | olare III             | 000, 00.        |            |          |

| НРМ         | Power supply circuit      | 81       | Input            | This pin                                                        | is used              | as a po     | wer cont   | rol pin of            | the pow         | er suppl   | y circui |

|             | select pin for LCD driver |          |                  | for the L                                                       | CD driv              | er.         |            |                       |                 |            |          |

|             |                           |          |                  | HPM =                                                           | H : Nor              | mal moo     | de         |                       |                 |            |          |

|             |                           |          |                  | HPM =                                                           | L : Higl             | n-power     | mode       |                       |                 |            |          |

| IRS         | Select pin for VLC1       | 83       | Input            |                                                                 |                      | to selec    | t the res  | istor that            | t is used       | to regula  | ate the  |

|             | regulating resistor       |          |                  |                                                                 | -                    |             |            |                       |                 |            |          |

|             |                           |          |                  |                                                                 |                      | ct on-chi   | •          |                       | <b>T</b> b = 1/ |            |          |

|             |                           |          |                  |                                                                 |                      |             |            | resistor.             |                 | -          | e IS     |

|             |                           |          |                  | U                                                               |                      | •           |            | external of           |                 |            | tod via  |

|             |                           |          |                  |                                                                 |                      |             |            | ot be sel<br>and. Ins |                 |            |          |

|             |                           |          |                  |                                                                 | ne settin            |             |            |                       |                 | 5 pi       |          |

| TEST1 to    | Test pins                 | 69 to 71 | Input            |                                                                 |                      | 0           | C tests.   | Normall               | y, these        | pins sho   | uld be   |

| TEST3       |                           |          |                  | left oper                                                       |                      |             |            |                       |                 |            |          |

| TEST4,TEST5 | Test pins                 | 72,73    | Output           | These a                                                         | re test p            | oins for l  | C tests.   | Normall               | y, these        | pins sho   | uld be   |

|             |                           |          |                  | left oper                                                       | n.                   |             |            |                       |                 |            |          |

#### 3.3 Driver System Pins

| Pin Symbol                             | Pin Name         | Pad No.                  | I/O    | Function Description                                                                                                                                                                             |

|----------------------------------------|------------------|--------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEG <sub>0</sub> to SEG <sub>131</sub> | Segment          | 122 to 253               | Output | Segment output pins                                                                                                                                                                              |

| COM <sub>0</sub> to COM <sub>63</sub>  | Common           | 87 to 118,<br>256 to 287 | •      | Common output pins                                                                                                                                                                               |

| COMS                                   | Indicator common | 288                      | Output | Common output pins for indicator<br>The same signal is output from pin 2.                                                                                                                        |

| Vrs                                    | Op amp inputs    | 53,54                    | Input  | These are input pins for the op amp that regulates the LCD driver voltage.<br>Leave the V <sub>RS</sub> pin open when using the on-chip power supply.                                            |

| Vr                                     | *                | 55,56                    |        | When not using the on-chip power supply, a reference voltage $V_{REG}$ must be input.<br>When using an external power supply, connect the VR pin to a resistor used to regulate the LCD voltage. |

| DUMMY1 to<br>DUMMY5                    | Dummy pins       | 1,85,86,<br>120,121      |        | Since these pins are not connected to any internal circuits, they should be left open when they are not being used.                                                                              |

#### 4. PIN I/O CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS

The input/output circuit type of each pin and recommended connection of unused pins are shown in the following table.

| Pin Name             | I/O          | Recommended Connection of Unused Pins                            | Notes |

|----------------------|--------------|------------------------------------------------------------------|-------|

| P,/S                 | Input        | Mode setting pin                                                 | 1     |

| /CS1                 | Input        | Connect to Vss                                                   |       |

| CS2                  | Input        | Connect to VDD                                                   |       |

| /RD(E)               | Input        | Connect to VDD (80 series interface),                            |       |

|                      |              | connect to V <sub>DD</sub> or V <sub>SS</sub> (serial interface) |       |

| /WR (R,/W)           | Input        | Connect to VDD or Vss (serial interface)                         |       |

| C86                  | Input        | Mode setting pin                                                 | 1     |

| D₀ to D₅             | Input/Output | Leave open (when using serial interface)                         | 4     |

| D <sub>6</sub> (SCL) | Input/Output |                                                                  |       |

| D7 (SI)              | Input/Output |                                                                  |       |

| A0                   | Input        | Data/command setting pin                                         | 2     |

| TESTOUT              | Output       | Leave open                                                       |       |

| /RES                 | Input        | Connect to VDD                                                   |       |

| CLS                  | Input        | Mode setting pin                                                 | 1     |

| FR                   | Input/Output | Leave open (when using master mode, M,/S = H)                    |       |

| FRS                  | Output       | Leave open                                                       |       |

| /DOF                 | Input/Output | Leave open (when using master mode, M,/S = H)                    |       |

| M,/S                 | Input        | Mode setting pin                                                 | 1     |

| CL                   | Input/Output | Display clock                                                    | 3     |

| НРМ                  | Input        | Mode setting pin                                                 | 1     |

| IRS                  | Input        | Mode setting pin                                                 | 1     |

| TEST1                | Input        | Leave open                                                       | 4     |

| TEST2                | Input        | Leave open                                                       | 4     |

| TEST3                | Input        | Leave open                                                       | 4     |

| TEST4                | Output       | Leave open                                                       |       |

| TEST5                | Output       | Leave open                                                       |       |

**Notes 1.** Connect to VDD or Vss according to the selected mode.

- 2. Input microcontroller output from VDD or Vss according to the selected register.

- 3. This pin is an output when M/S = H and CLS = H but should otherwise be used to input the display clock.

- 4. These pins are pulled down to Vss in the IC.

#### 5. DESCRIPTION OF FUNCTIONS

#### 5.1 MPU Interface

#### 5.1.1 Select interface type

The  $\mu$  PD16682 transfers data either via an 8-bit bidirectional data bus (D7 to D0) or via a serial data input (SI). The P,/S pin can be set to either high or low levels to select 8-bit parallel data input or serial data input, as shown in the table below.

| P,/S              | /CS1 | CS2 | A0 | /RD    | /WR    | C86   | D7 | D <sub>6</sub> | D5 - D0 |

|-------------------|------|-----|----|--------|--------|-------|----|----------------|---------|

| H: Parallel input | /CS1 | CS2 | A0 | /RD    | /WR    | C86   | D7 | D <sub>6</sub> | D5 -D0  |

| L: Serial input   | /CS1 | CS2 | A0 | Note 1 | Note 1 | Note1 | SI | SCL            | Note2   |

**Notes 1.** Fix this pin as either H or L.

2. High impedance

#### 5.1.2 Parallel interface

If the parallel interface has been selected (P,/S = H), setting the C86 pin either high or low determines whether to connect directly to the 80 series MPU or the 68 series MPU, as shown in the table below.

| P,/S                 | /CS1 | CS2 | A0 | /RD | D7 - D0 |

|----------------------|------|-----|----|-----|---------|

| H: 68 series MPU bus | /CS1 | CS2 | A0 | E   | D7 - D0 |

| L: 80 series MPU bus | /CS1 | CS2 | A0 | /RD | D7 - D0 |

The data bus signal can be identified according to the combination of A0, /RD(E), and /WR (R,/W) signals, as shown in the table below.

| Common | 68 Series | 80 Series |   | Function                     |

|--------|-----------|-----------|---|------------------------------|

| A0     | R,/W      | /RD /WR   |   |                              |

| н      | Н         | L         | Н | Read display data            |

| н      | L         | Н         | L | Write display data           |

| L      | Н         | L         | Н | Read status                  |

| L      | L         | Н         | L | Write control data (command) |

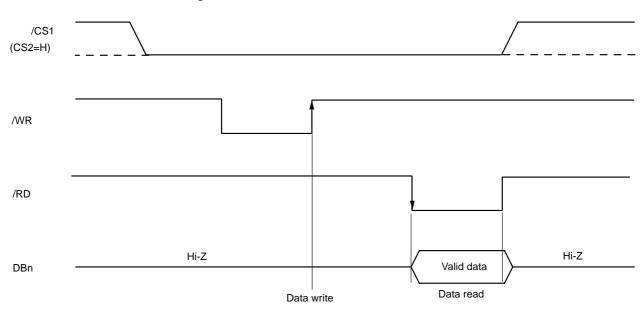

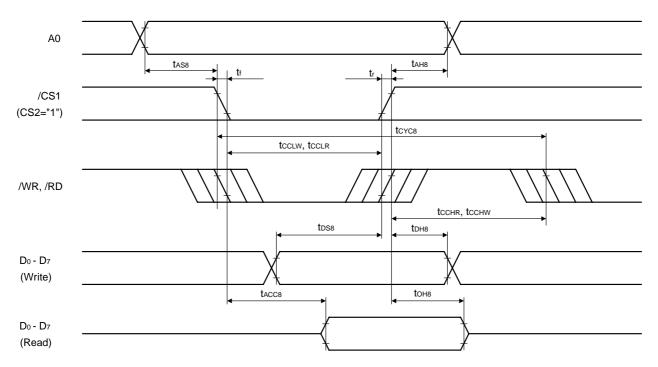

#### (1) 80 Series Parallel Interface

When 80 series parallel data transfer has been selected, data is written to the  $\mu$  PD16682 at the rising edge of the /WR signal. The data is output to the data bus when the /RD signal is L.

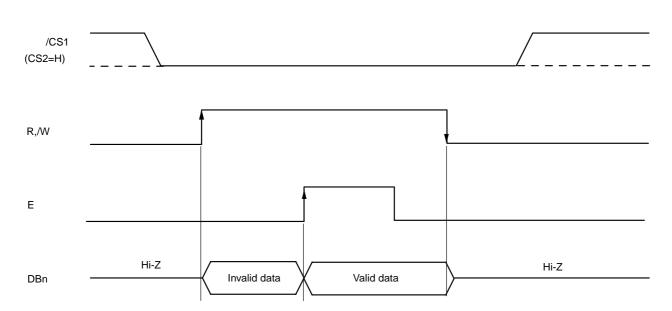

#### (2) 68 Series Parallel Interface

When 68 series parallel data transfer has been selected, data is written at the falling edge of the E signal when the R,/W signal is L. During the data read operation, the data bus enters the output status when the R,/W signal is H, outputs valid data at the rising edge of the E signal, and enters the high-impedance state at the falling edge of the R,/W signal (R,/W = L)

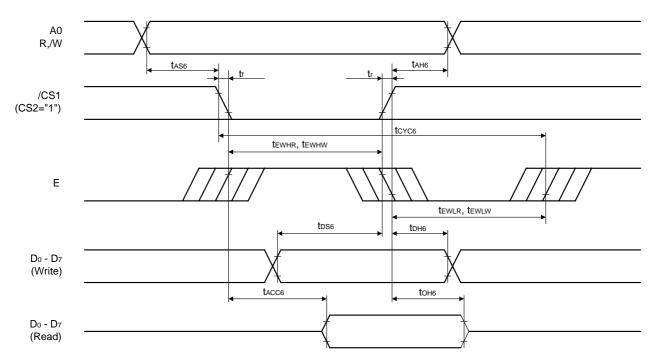

#### 5.1.3 Serial interface

NEC

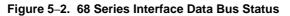

If the serial interface has been selected (P,/S = L) and if the chip is in the active state (/CS1 = L and CS2 = H), both serial data input (SI) and serial clock input (SCL) can be received. The serial interface includes an 8-bit shift register and a 3-bit counter. Serial data is captured at the rising edge of the serial clock and is clocked in via the serial data input pins in sequence from D<sub>7</sub> to D<sub>0</sub>. At the rising edge of the eighth serial clock, data is converted to 8-bit parallel data.

Input via the A0 pin can be used to determine whether the input serial data is display data or a command (display data when A0 = H, command when A0 = L). The timing for reading and identifying input via A0 occurs at the rising edge of the "eighth x n" serial clock once the chip's status is active.

A serial interface signal chart is shown below.

Figure 5–3. Serial Interface chart

Remarks1. When the chip's status is inactive, the shift register and counter are both reset to their initial values.

2. Data cannot be read when using the serial interface.

**3.** For the SCL signal, caution is advised concerning the wire's terminating reflection and noise from external sources. We recommend to check the operation on the actual equipment.

#### 5.1.4 Chip select

The  $\mu$  PD16682 has two chip select pins (/CS1 and CS2). The MPU interface or serial interface can be used only when /CS1 = L and CS2 = H.

When the chip select pin is inactive,  $D_7$  to  $D_0$  are set to high impedance (invalid) and input of A0, /RD, or /WR is invalid. If the serial interface has been selected, the shift register and counter are both reset.

#### 5.1.5 Display data RAM and internal register access

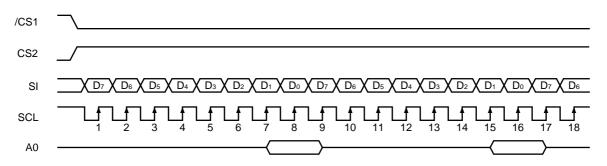

Access to the  $\mu$  PD16682 from the MPU supports high-speed data transfers since the cycle time (tcyc) is met and there is no need for wait time.

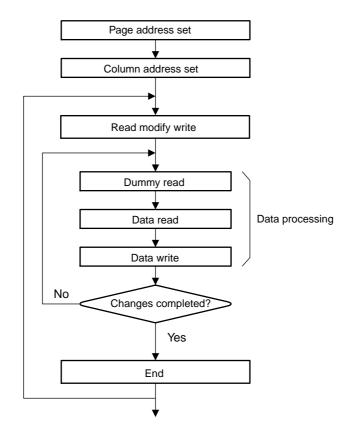

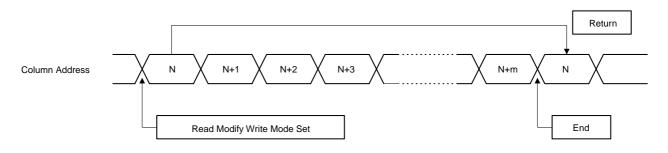

When data transfer occurs between the  $\mu$  PD16682 and the MPU, the data is held in a bus holder belonging to the internal data bus and is written to the display data RAM before the next data write cycle. When the MPU reads the contents of the display data RAM, the data read during the first data read cycle (dummy cycle) is first held in the bus holder and is read from the bus holder to the system bus during the next data read cycle.

Note with caution that, due to constraints on the read sequence for the display data RAM, when the address is set, the data is not output from the address specified by the next read command but rather is output to the address specified during the second data read operation. Consequently, one dummy read operation is strictly required after setting an address or after a write cycle. Figure 5–4 illustrates this situation.

Figure 5–4. Write and Read Operations

Data Sheet S13368EJ4V0DS

#### 6. DISPLAY DATA RAM

#### 6.1 Display Data RAM

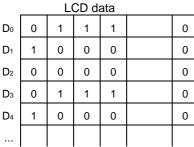

This is the RAM that is used to store the display's dot data. The RAM configuration is 65 (8 pages x 8 bits + 1) x 132 bits. Any specified bit can be accessed by selecting the corresponding page address and column address.

As is shown in Figure 6–1 below, the display data ( $D_7$  to  $D_0$ ) from the MPU corresponds to the common direction in the LCD, so that if a multiple set of  $\mu$  PD16682 chips is used, there are fewer constraints on transfers of display data and relatively more freedom for display configurations.

The MPU accesses the display data RAM for read/write operations via the I/O buffer, and these operations are independent of the LCD driver signal read operations. Therefore, there are absolutely no adverse effects (such as flicker) in the display when display data RAM is accessed asynchronously in relation to the LCD contents.

Figure 6–1. LCD Data and LCD Display

|                  | LCD display |  |  |  |  |  |  |  |  |  |  |  |  |

|------------------|-------------|--|--|--|--|--|--|--|--|--|--|--|--|

| COM <sub>0</sub> |             |  |  |  |  |  |  |  |  |  |  |  |  |

| COM <sub>1</sub> |             |  |  |  |  |  |  |  |  |  |  |  |  |

| COM <sub>2</sub> |             |  |  |  |  |  |  |  |  |  |  |  |  |

| COM <sub>3</sub> |             |  |  |  |  |  |  |  |  |  |  |  |  |

| COM <sub>4</sub> |             |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |             |  |  |  |  |  |  |  |  |  |  |  |  |

#### 6.2 Page Address Circuit

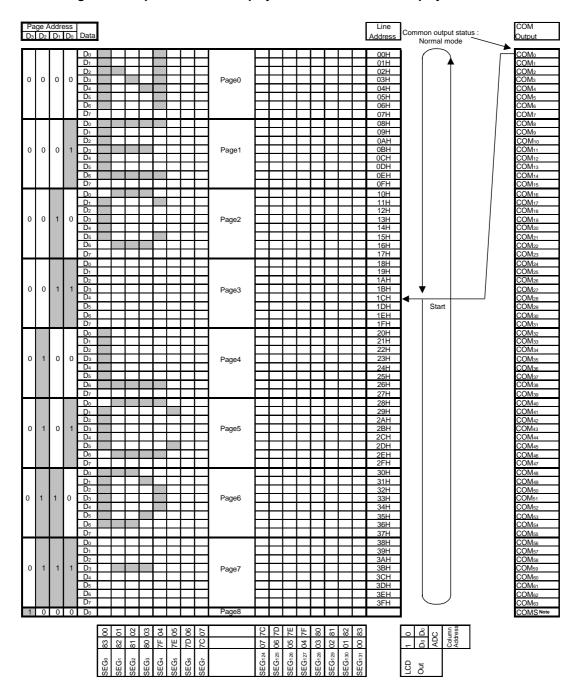

The page address set command specifies the page address in the display data RAM, as is shown in Figure 6–2. To access a different page, simply specify a different page address using this command.

Page address 8 ( $D_3$ , $D_2$ , $D_1$ , $D_0$  = 1,0,0,0) is a RAM area that is used exclusively for indicator, so only display data  $D_0$  is valid.

#### 6.3 Column Address Circuit

The column address set command specifies the column address in the display data RAM, as is shown in Figure 6–2. The specified column address is incremented each time a display data read or write command is input, so the MPU is able to successively access display data.

Incrementation of the column address stops at 83H. The column address and page address are mutually independent, which means that to switch from column 83H on page 0 to column 00H on page 1, both the page address and column address must be separately specified again.

Also, as is shown in Table 6–1, the ADC command (segment driver direction select command) can be used to invert the correspondence between the display data RAM's column address and segment output. This reduces the number of IC layout constraints that are imposed when setting up the LCD module.

Table 6–1. Relation between Display Data RAM Column Address and Segment Output

| SEG Ou            | utput | SEG₀ |               |                |               | SEG131 |

|-------------------|-------|------|---------------|----------------|---------------|--------|

| ADC               | "0"   | 00H  | $\rightarrow$ | Column Address | $\rightarrow$ | 83H    |

| (D <sub>0</sub> ) | "1"   | 83H  | $\leftarrow$  | Column Address | $\leftarrow$  | 00H    |

#### 6.4 Line Address Circuit

NEC

As is shown in Figure 6–2, the line address circuit specifies the line address that corresponds to a COM output for displaying the contents of display data RAM. The display start line address set command usually specifies the highest line in the display (corresponding to the COM<sub>0</sub> output when in normal mode or the COM<sub>63</sub> output when in inverted mode). Thus, there are 65 lines in the direction of incrementation of line address starting from the specified display start line address.

The screen can be scrolled by dynamically changing the line address via the display start line address set command.

Note COMS accesses the 65th line regardless of the display start line address.

Data Sheet S13368EJ4V0DS

#### 6.5 Display Data Latch Circuit

The display data latch circuit is used for temporary storage of display data that has been output to the LCD driver circuit from the display data RAM.

The commands that are used to set normal/inverted display modes, display ON/OFF status, and display all ON/OFF status are commands that control data in this latch so that there is no modification of the data in the display data RAM.

#### 7. OSCILLATION CIRCUIT

This is a CR-type oscillation circuit that generates the display clock. The oscillation circuit is valid only when CLS = H. When CLS = L, oscillation is stopped and the display clock is input via the CL pin.

#### 8. DISPLAY TIMING GENERATOR

The display timing generator generates timing signals from the display clock to the line address circuit and the display data latch circuit. Display data is latched into the display data latch circuit in synch with the display clock and is output via segment driver output pins. Reading of the display data is completely independent of the MPU's accessing of the display data RAM. Consequently, there are no adverse effects (such as flicker) on the LCD panel even when the display data RAM is accessed asynchronously in relation to the LCD contents.

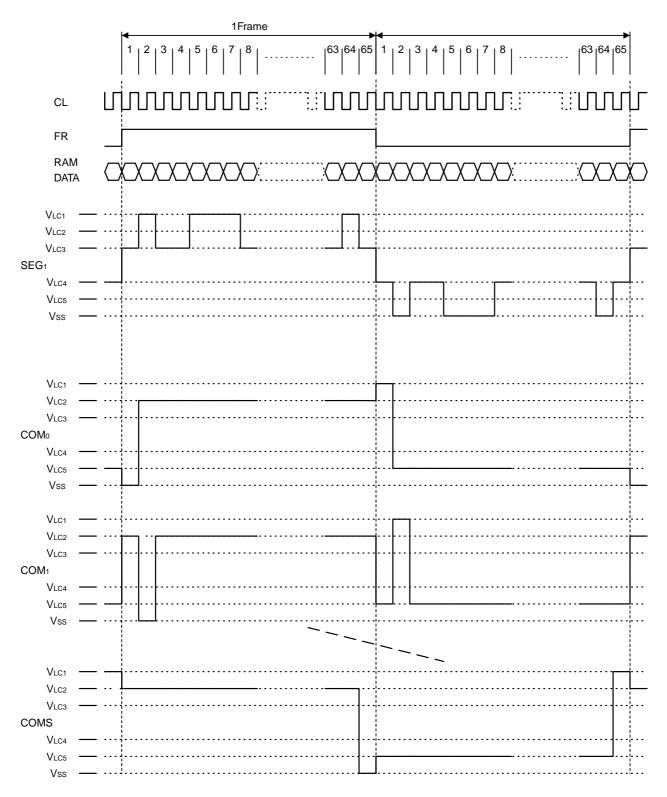

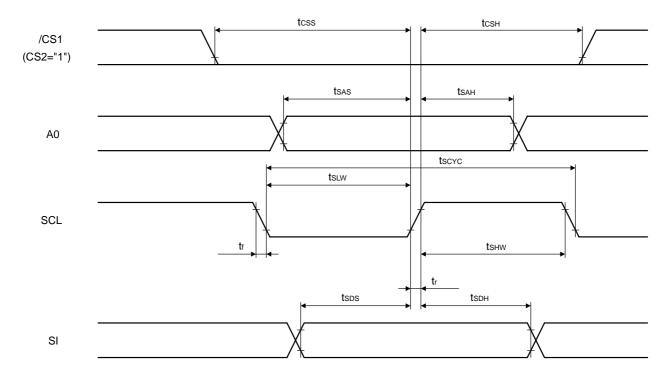

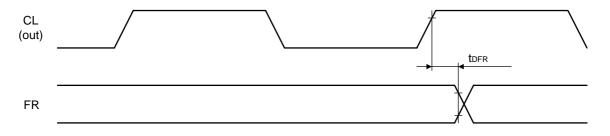

The internal common timing and LCD's AC conversion signal (FR) are both generated from the display clock. As is shown in Figure 8–1, a drive waveform based on the two-frame AC drive method is generated for the LCD driver circuit.

If a multiple set of  $\mu$  PD16682 chips is used, the display timing signals (FR, CL, and /DOF) for the slave side must be supplied from the master side.

|                   | Operation Mode                                   |        |        |        |  |  |

|-------------------|--------------------------------------------------|--------|--------|--------|--|--|

| Master (M,/S = H) | On-chip oscillation circuit is valid (CLS = H)   | Output | Output | Output |  |  |

|                   | On-chip oscillation circuit is invalid (CLS = L) | Output | Input  | Output |  |  |

| Slave (M,/S = L)  | On-chip oscillation circuit is invalid (CLS = H) | Input  | Input  | Input  |  |  |

|                   | On-chip oscillation circuit is invalid (CLS = L) | Input  | Input  | Input  |  |  |

Figure 8–1. Drive Waveform when Using Two-Frame AC Drive Method

Data Sheet S13368EJ4V0DS

#### 9. COMMON OUTPUT STATUS SELECT CIRCUIT

With the  $\mu$  PD16682, the common output status select command can be used to set the scan direction for COM outputs (see Table 9–1). As a result, there are fewer IC layout constraints when setting up the LCD module.

| Status             | COM               | Scan Direction |                   |

|--------------------|-------------------|----------------|-------------------|

| Normal (forward)   | COM₀              | $\rightarrow$  | COM <sub>63</sub> |

| Inverted (reverse) | COM <sub>63</sub> | $\rightarrow$  | COMo              |

Table 9–1.

Setting of Scan Direction for COM Outputs

#### **10. POWER SUPPLY CIRCUIT**

#### 10.1 Power Supply Circuit

The power supply circuit, which supplies the voltage needed to drive the LCD, includes a booster circuit, voltage regulator circuit, and voltage follower circuit.

The power control set command is used to control the ON/OFF status of the power supply circuit's booster circuit, voltage regulator circuit (V regulator circuit), and voltage follower circuit (V/F circuit). This makes it possible to jointly use an external power supply along with certain functions of the on-chip power supply. Table 10–1 shows the function that controls the 3-bit data in the power control set command and Table 10–2 shows a reference chart of combinations.

| Table 10–1. | <b>Control Values S</b> | Set to Bits in Power | Control Set Command |

|-------------|-------------------------|----------------------|---------------------|

|-------------|-------------------------|----------------------|---------------------|

|    | Item                                  | Status |     |  |  |

|----|---------------------------------------|--------|-----|--|--|

|    |                                       | Н      | L   |  |  |

| D2 | Booster circuit control bit           | ON     | OFF |  |  |

| D1 | Voltage regulator circuit control bit | ON     | OFF |  |  |

| Do | Voltage follower circuit control bit  | ON     | OFF |  |  |

| Use Status                                             | D2 | D1 | Do | Booster<br>Circuit | V Regulator<br>Circuit | V/F Circuit | External Power<br>Supply Input | Booster-<br>related Pin |

|--------------------------------------------------------|----|----|----|--------------------|------------------------|-------------|--------------------------------|-------------------------|

| <1> Use on-chip power supply                           | Н  | Н  | н  | 0                  | 0                      | 0           | Vdd2                           | Used                    |

| <2> Use V regulator<br>circuit and V/F circuit<br>only | L  | Н  | Н  | ×                  | 0                      | 0           | VLCD                           | Open                    |

| <3> Use V/F circuit only                               | L  | L  | Н  | ×                  | ×                      | 0           | VLC1                           | Open                    |

| <4> Use External power<br>supply only                  | L  | L  | L  | ×                  | ×                      | ×           | Vlc1 <b>to</b> Vlc5            | Open                    |

Table 10–2.

Reference Chart of Combinations

**Remarks 1.** The booster-related pins are indicated as pins  $C_1^+$ ,  $C_1^-$ ,  $C_2^-$ ,  $C_3^-$ , and  $C_3^-$ .

**2.** Although combinations other than those shown above are possible, they have no practical uses and therefore cannot be recommended.

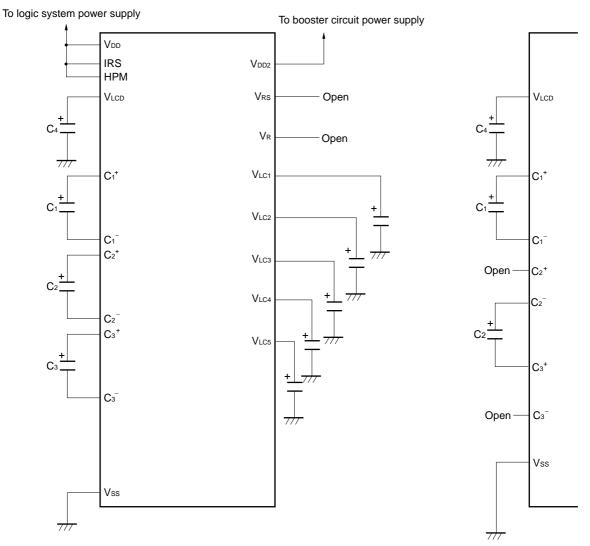

#### 10.2 Booster circuit

NEC

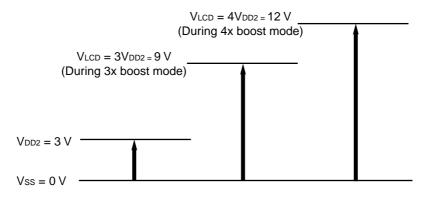

3x and 4x booster circuits have been incorporated in chip to generate the current driving the LCD.

When using the internal power supply, connect the booster-related capacitor between  $C_1^+$  and  $C_1^-$ ,  $C_2^+$  and  $C_2^-$ , and  $C_3^+$  and  $C_3^-$ . Also, connect the level stabilization-related capacitor between  $V_{LCD}$  and  $V_{SS}$  and set  $D_2$  high to boost the potential between  $V_{DD2}$  and  $V_{SS}$  from 3 to 4 times.

Since the booster circuit uses signals from the internal oscillation circuit, the oscillation circuit must be operating. The relation between the boosted voltage and the potential is described below.

The  $C_1^+$ ,  $C_1^-$ ,  $C_2^+$ ,  $C_2^-$ ,  $C_3^+$ ,  $C_3^-$ , and  $V_{DD2}$  pins all relate to the booster circuit, so the wire impedance should be minimized.

Figure 10–1. 3x and 4x Booster Circuits

## Caution When set to 3x boost mode, connect booster-related capacitors between $C_2^-$ and $C_3^+$ and between $C_1^+$ and $C_1^-$ .

#### 10.3 Voltage Regulator Circuit

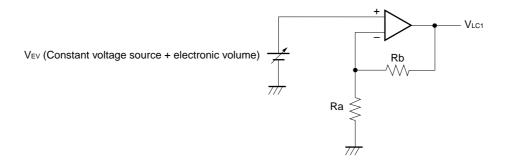

The boost voltage that was generated at V<sub>LCD</sub> is output via the voltage regulator circuit as the LCD drive voltage V<sub>LC1</sub>. Since the  $\mu$  PD16682 has a 64-level electronic volume function and an on-chip resistor for V<sub>LC1</sub> voltage regulation, various components can be used to configure a highly accurate voltage regulator circuit.

#### 10.3.1 Use of on-chip resistor for VLC1 voltage regulation

The on-chip resistor for V<sub>LC1</sub> voltage regulation and the electronic volume function can be used to regulate the darkness of the LCD contents, not only by adding an external resistor but also by controlling the LCD drive voltage V<sub>LC1</sub> by using commands only. The V<sub>LC1</sub> voltage can be determined using equation 10–1 as within the range of V<sub>LC1</sub> < V<sub>LCD</sub>.

#### Equation 10-1.

$$V_{LC1} = (1 + \frac{Rb}{Ra})V_{EV}$$

The equation for determining VEV varies according to the product code (temperature gradient).

$$V_{EV} = \frac{162}{203} (1 - \frac{\alpha}{162}) V_{REG} (-001 \text{ code}, -0.05\% / °C)$$

$$V_{EV} = \frac{162}{178} (1 - \frac{\alpha}{162}) V_{REG} (-002 \text{ code}, -0.1\% / °C)$$

$$V_{EV} = (1 - \frac{\alpha}{162}) V_{REG} (-003 \text{ code}, -0.15\% / °C)$$

$$V_{EV} = \frac{162}{236} (1 - \frac{\alpha}{162}) V_{REG} (-004 \text{ code}, 0\% / °C)$$

$V_{REG}$  is the IC's internal constant voltage source, whose voltage values (at  $T_A = 25^{\circ}C$ ) are listed in Table 10–3 below.

Table 10-3. VREG

| Product Code | Temperature Gradient (%/°C) | Vreg (V) |  |  |

|--------------|-----------------------------|----------|--|--|

| -001         | -0.05                       | 2.08     |  |  |

| -002         | -0.1                        | 1.84     |  |  |

| -003         | -0.15                       | 1.62     |  |  |

| -004         | 0                           | 2.39     |  |  |

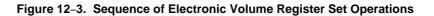

Given  $\alpha$  as the electronic volume command value, when data is set to the 6-bit electronic volume register, one of 64 statuses is set. Values for  $\alpha$  corresponding to various electronic volume register settings are listed in Table 10–4 below.

| D₅ | D4 | D3 | D2 | D1 | Do | α  |

|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 0  | 63 |

| 0  | 0  | 0  | 0  | 0  | 1  | 62 |

| 0  | 0  | 0  | 0  | 1  | 1  | 61 |

| 0  | 0  | 0  | 0  | 1  | 1  | 60 |

| :  | :  | :  | :  | :  |    | :  |

| 1  | 1  | 1  | 1  | 0  | 1  | 2  |

| 1  | 1  | 1  | 1  | 1  | 0  | 1  |

| 1  | 1  | 1  | 1  | 1  | 1  | 0  |

Table 10-4. α Values Determined by Electronic Volume Register Settings

Rb/Ra is an on-chip resistance factor used for the  $V_{LC1}$  voltage regulator. This factor can be controlled among eight levels using the  $V_{LC1}$  voltage regulator resistance factor set command. Table 10–5 lists reference values for (1+Rb/Ra) which are set when 3-bit data is set to the  $V_{LC1}$  voltage regulator resistance factor register.

|    | Reference Value |    |     |

|----|-----------------|----|-----|

| D3 | D2              | D1 |     |

| 0  | 0               | 0  | 3.5 |

| 0  | 0               | 1  | 4.0 |

| 0  | 1               | 0  | 4.5 |

| 0  | 1               | 1  | 5.0 |

| 1  | 0               | 0  | 5.5 |

| 1  | 0               | 1  | 6.0 |

| 1  | 1               | 0  | 6.5 |

| 1  | 1               | 1  | 7.0 |

Table 10–5. Reference Values for (1 + Rb/Ra)

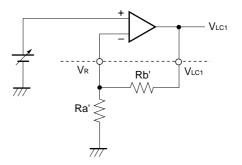

#### 10.3.2 When using external resistor (not using on-chip resistor for VLc1 voltage regulator)